Dear Obsidian Support Team,

I hope this message finds you wel ![]() l. I am writing to report a bug that I have encountered while using the Obsidian app.

l. I am writing to report a bug that I have encountered while using the Obsidian app.

Bug Description: When using code blocks to display Verilog code, I noticed that the nonblocking assignment symbol “<=” is incorrectly formatted as a less than or equal to symbol “≤”. This formatting change is not consistent with Verilog coding conventions and can lead to confusion for users familiar with Verilog syntax.

Steps to Reproduce:

- Open Obsidian and create a new note.

- Insert a code block and enter Verilog code containing nonblocking assignment statements using the “<=” symbol.

- Preview or render the note to observe the formatting of the Verilog code within the code block.

Expected Behavior: The Verilog code within the code block should display the nonblocking assignment symbol “<=” accurately and consistently.

Actual Behavior: The nonblocking assignment symbol “<=” is displayed as a less than or equal to symbol “≤” within the code block.

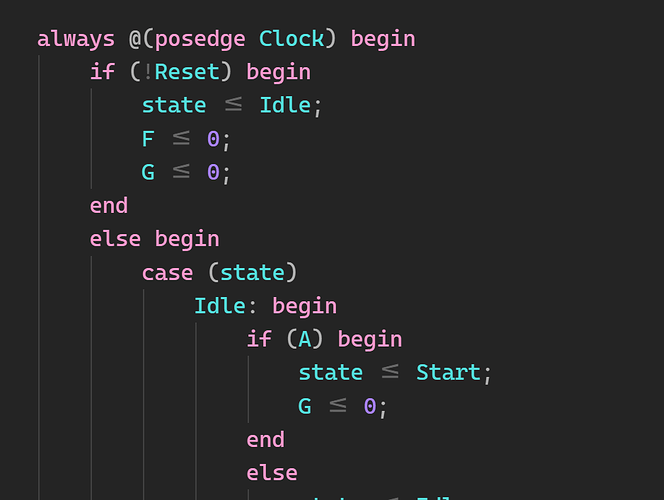

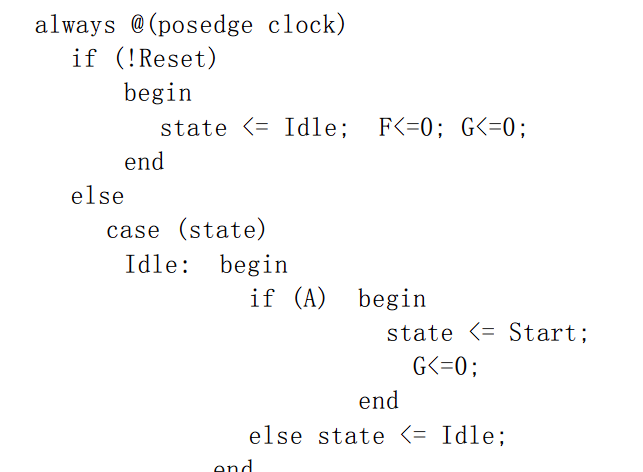

Screenshot:

Correctly.

Uncorrectly.

Please note that this issue affects the readability and usability of Verilog code within Obsidian, especially for users working extensively with Verilog designs.

I kindly request that your development team investigate and address this issue in a future update of the Obsidian app. If you require any further information or clarification regarding this bug report, please feel free to contact me.

Thank you for your attention to this matter. ![]()