Steps to reproduce

In my case, when I nest a SystemVerilog code block inside a callout, its code syntax disappeared; the code syntax for SystemVerilog is normal when placing it outside a callout in editing mode, but disappearing in reading mode.

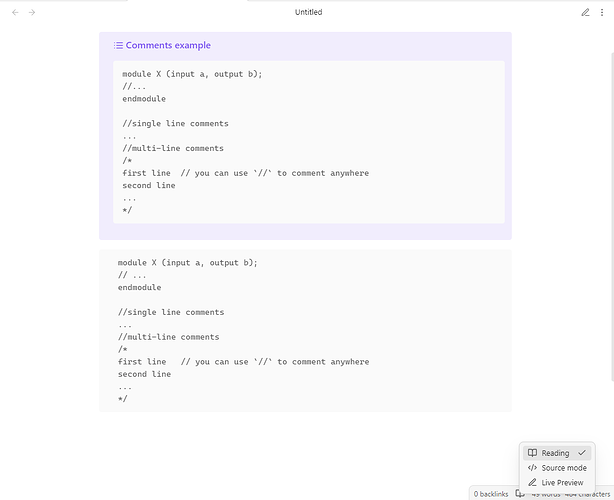

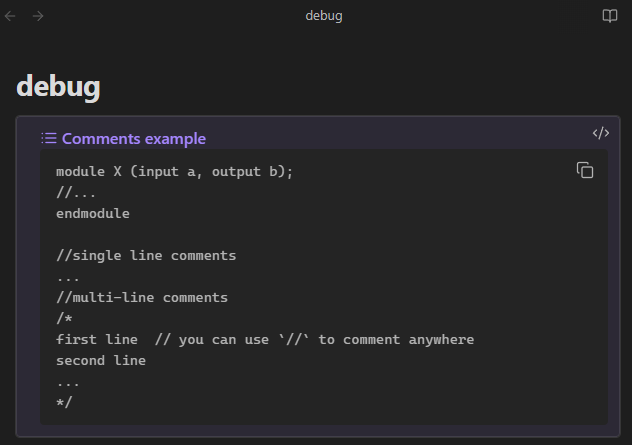

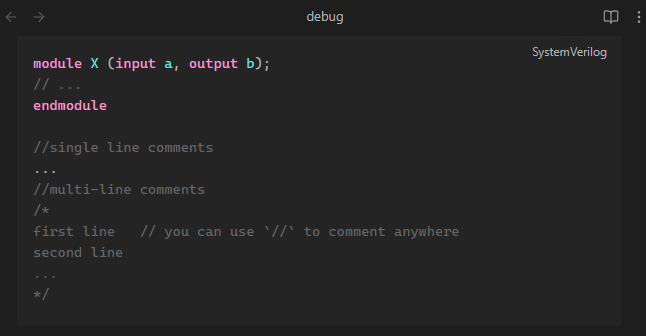

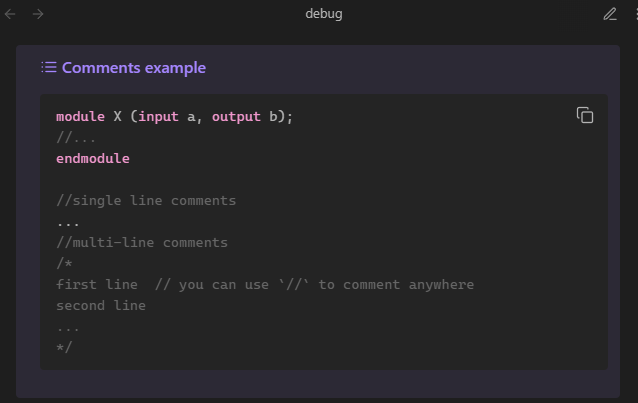

The example code and screenshots are given as following (testing in the sandbox vault):

- code block inside a callout

> [!example] Comments example

> ```SystemVerilog

> module X (input a, output b);

> //...

> endmodule

>

> //single line comments

> ...

> //multi-line comments

> /*

> first line // you can use `//` to comment anywhere

> second line

> ...

> */

> ```

- code block outside a callout

```systemverilog

module X (input a, output b);

// ...

endmodule

//single line comments

...

//multi-line comments

/*

first line // you can use `//` to comment anywhere

second line

...

*/

```

In editing mode

In reading mode

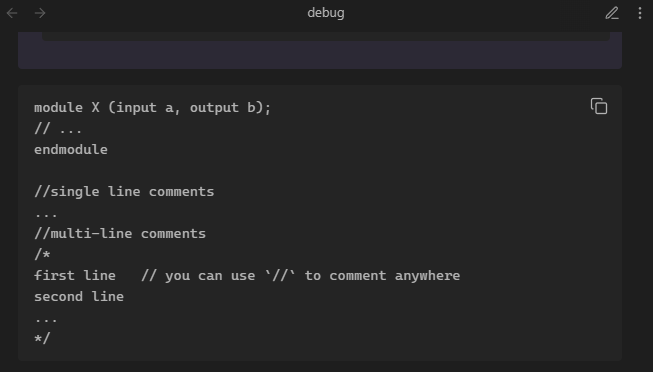

- change the code block to another language, for example Verilog, the displaying is normal.

> [!example] Comments example

> ```Verilog

> module X (input a, output b);

> //...

> endmodule

>

> //single line comments

> ...

> //multi-line comments

> /*

> first line // you can use `//` to comment anywhere

> second line

> ...

> */

> ```

Did you follow the troubleshooting guide? [Y/N]

Y

Expected result

The apearance of a code block inside a callout is normal for all supported coding language.

Actual result

Environment

SYSTEM INFO:

Obsidian version: v1.7.7

Installer version: v1.7.5

Operating system: Windows 11 Home 10.0.22631

Login status: logged in

Language: en

Catalyst license: none

Insider build toggle: off

Live preview: on

Base theme: dark

Community theme: none

Snippets enabled: 0

Restricted mode: on

RECOMMENDATIONS:

none

Additional information

Seen reproduce part